Ministry of Electronics & IT

Minister Rajeev Chandrasekhar flags off the Nationwide Roadshow on Digital India RISC-V (DIR-V) Program

“RISC-V (DIR-V) Program will offer opportunities to students, startups & entrepreneurs, further catalysing the semiconductor ecosystem in India”: MoS Rajeev Chandrasekhar

SHAKTI and VEGA Processors Anchor DIR-V Ecosystem, Enabling Collaboration with Start-ups and Entrepreneurs

Innovation, functionality, performance — these are the mantras for future of RISC-V (DIR-V) Program

“Future is Bright, Future is DIR-V for India”: MoS Rajeev Chandrasekhar

Posted On:

17 NOV 2023 1:06PM by PIB Delhi

Union Minister of State for Skill Development & Entrepreneurship and Electronics & IT Shri Rajeev Chandrasekhar today flagged off the Nationwide Roadshow on Digital India RISC-V (DIR-V) Program. This roadshow is being jointly organized by C-DAC, IEEE India Council and Ministry of Electronics & IT (MeitY) on 17-18 November 2023, with participation from global leaders in the RISC-V design area.

As part of the Digital India RISC-V (DIR-V) program announced by Minister Rajeev Chandrasekhar in 2022, successful tapeouts were carried out for – (a) 32-bit/ 64-bit SHAKTI Processors at 180nm (SCL foundry) and 22nm (Intel foundry) by IIT Madras, (b) 32-bit AJIT Processor at 180nm (SCL foundry) by IIT Bombay, and (c) 32-bit VEGA Processors at 130nm (Silterra foundry) and 64-bit VEGA Processors at 180nm (SCL Mohali) by C-DAC.

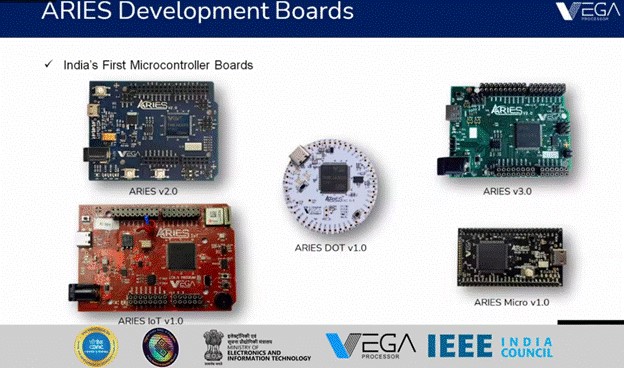

C-DAC has now created a series of ARIES Development Boards based on VEGA Processor Chip viz. ARIES Micro, ARIES V2, ARIES V3, ARIES IoT and ARIES DOT. These development kits are fully indigenous and 'Made in India' products targeted for learning, embedded system design, and IoT applications. The boards, built upon the RISC-V ISA-compliant VEGA Processor, come with easy-to-use hardware and software.

According to Minister Rajeev Chandrasekhar, this program is playing a pivotal role in realizing the vision laid by PM Modi of creating and adoption open-source technologies.

Shri Rajeev Chandrasekhar said, “Our prime focus is to enable the growth of the DIR-V ecosystem, aiming for India to emerge as a leading nation in innovating around the DIR-V family of chips and systems. This program will play a pivotal role in realizing Prime Minister Narendra Modi ji’s vision of creating and adopting open-source technologies. Start-ups, students, and entrepreneurs will play crucial roles in developing DIR-V-based chips and systems, ultimately contributing to India becoming a Semiconductor Nation,”

The Minister also highlighted how this program will ensure DIR V-based chips and systems are integrated into various digital products we use daily. “In the last 50 years, computer processors have evolved with many ideas, eventually settling on one main design that everyone adopts. Now, our focus is on the DIR-V program, envisioning a future where DIR V-based chips and systems are integrated into various digital products we use daily. India has also embraced RISC-V in flagship government projects, witnessing growth in startup research and innovation around RISC-V. India hosts several startups working on RISC-V-based designs, which are also part of MeitY’s futureDESIGN initiative. For instance, Incore Semiconductors is developing configurable RISC-V processor cores, Mindgrove Technologies is working on fault-tolerant systems, and Morphing Machines is developing multi-core reconfigurable systems,” the Minister further added.

The roadshow aims to provide 1500 participants with valuable insights into the DIR-V VEGA series of processors and their ecosystem, covering both theoretical and practical aspects, including the use of development boards, SDK, and application development. Hands-on sessions will be conducted using the ARIES development boards, which are Arduino-compatible. It will also feature addresses by prominent global leaders, including Prof. Krste Asanovic, Chief Architect at SiFive & Professor at UC Berkeley; Calista Redmond, CEO of RISC-V International; Balaji Baktha, CEO of Ventana Micro Systems; Prof. Kamakoti, Director at IIT Madras and Chief Architect of the DIR-V Program.

This event is being concurrently held at 15 academic institutions across India namely: Alliance University - Bangalore, Amrita University - Bangalore, Birla Institute of Technology and Science, Pilani - Hyderabad, Chandigarh University - Punjab, Cochin University of Science and Technology - Kerala, Guru Tegh Bahadur Institute of Technology - Delhi, Indian Institute of Information Technology - Madhya Pradesh, KIET Group of Institutions - Ghaziabad, Koneru Lakshmaiah University - Andhra Pradesh, Mody University of Science and Technology - Rajasthan, Netaji Subhash Engineering College - West Bengal, PSG College of Technology - Tamil Nadu, Thakur College of Engineering and Technology - Maharashtra, Vardhaman College of Engineering – Telangana and Vellore Institute of Technology (VIT) - Tamil Nadu.

*******

DK/DK/SMP

(Release ID: 1977576)

Visitor Counter : 2748